### OPEN PLATFORM MANAGEMENT ARCHITECTURE

#### SPECIFICATION LICENSE AGREEMENT

This Open Platform Management Architecture Specification License Agreement ("Agreement") is made by Advanced Micro Devices, Inc., a Delaware corporation, having its principal place of business at One AMD Place, Sunnyvale, California, 94088 ("AMD"), and the entity named on the signature page of this Agreement ("Adopter"). This Agreement is effective as of the date a fully executed original has been received by AMD ("Effective Date").

### BACKGROUND

A. AMD has developed a platform architecture which is designed to modularize the platform hardware manageability subsystem for servers, the Open Platform Management Architecture. AMD desires to provide the OPMA (defined below) specification to various vendors and suppliers in a manner that enables compatibility between different vendors' hardware and software designs implementing OPMA.

B. AMD is the owner or licensee of certain intellectual property rights covering OPMA and the OPMA Specification and is willing to license such rights to Adopter under the terms and conditions set forth in this Agreement.

NOW, THEREFORE, in consideration of the mutual covenants and conditions contained herein and for other good and valuable consideration, the receipt and sufficiency of which are hereby acknowledged, and intending to be legally bound hereby, the parties hereto agree as follows:

### AGREEMENT

### Article 1. Ownership and License Grants

1.1 <u>Ownership</u>. Adopter hereby acknowledges and agrees that AMD, AMD Affiliates, and AMD's licensors shall retain ownership of all worldwide rights, titles, and interests in and to OPMA and the OPMA Specification, and all related intellectual property rights embodied therein, subject to the licenses granted to Adopter in Section 1.2 below.

1.2 <u>Licenses</u>. As of the Effective Date, the following licenses are granted by Adopter to AMD and all Fellow Adopters (as provided in Section 1.2.2), and the grants of AMD and all Fellow Adopters shall extend to Adopter. In each case, the party (AMD, Adopter, or Fellow Adopter) granting the license is referred to as the "Grantor," and the party (AMD, Adopter, or Fellow Adopter) receiving the license is referred to as the "Grantee." "Fellow Adopters" are all other entities which have executed, at any time, an agreement substantially similar to this Agreement and delivered it to AMD.

1.2.1 <u>OPMA.</u> Subject to the terms and conditions of this Agreement, Grantor hereby grants to Grantees a worldwide, non-exclusive, royalty free, non-transferable license under Grantor's Necessary Claims, to make, have made, use, import, sell, offer to sell, lease, and otherwise dispose of Compliant Portions, provided that such license shall not extend to any part or function of a product that is itself not part of a Compliant Portion.

1.2.2 <u>Extension to Fellow Adopters</u>. AMD may extend the licenses set forth in this Section 1.2 to any third party Fellow Adopter subject to the terms and conditions set forth in this Agreement, including but not limited to those set forth in Section 1.3 below.

1.3 <u>No Implied Licenses</u>. Except as expressly provided in this Agreement, no other rights are granted by Grantor hereunder by implication, estoppel or otherwise. All rights not expressly granted by Grantor are reserved to Grantor.

### Article 2. Usage of Adopter Name

2.1 <u>Use of Adopter Name</u>. AMD shall have the right to include Adopter's name in any lists, published by AMD, of entities licensing OPMA.

### Article 3. Confidentiality

3.1 <u>Nondisclosure</u>. The parties acknowledge that it may be necessary for AMD to disclose to Adopter certain confidential and/or proprietary information ("Confidential Information") to effectuate the purpose of this Agreement. Confidential Information shall include (a) information provided by AMD to Adopter hereunder that AMD identifies in writing as confidential or proprietary information, (b) any information provided hereunder, whether orally or in writing, which Adopter knows or has reason to know is Confidential Information of AMD, and (c) until made publicly available by AMD, the OPMA Specification and this Agreement. Adopter acknowledges that all rights to Confidential Information are reserved by AMD, and unless otherwise provided in this Agreement, Adopter may not disclose or disseminate such Confidential Information to anyone other than its employees or contractors with a need to know such Confidential Information for purposes of this Agreement. Adopter will protect the Confidential Information by using the same degree of care, but no less than a reasonable degree of care, to prevent the unauthorized use, dissemination, or disclosure of the Confidential Information as it uses to protect its own confidential information of a like nature.

Feedback. Adopter may, but is not obligated to, provide AMD with feedback, 3.2 suggestions, and improvements regarding the OPMA Specification and drafts thereof for possible incorporation by AMD or its designee into future versions of the OPMA Specification. Such feedback, suggestions, and improvements provided to AMD or its designee in writing or through an Electronic Feedback Forum (defined below in Section 3.3) shall be referred to herein as "Feedback." AMD or its designee shall be free to incorporate any and all Feedback into the OPMA Specification, and reserves the right to determine, in its sole discretion, the contents of the OPMA Specification. Adopter hereby grants to AMD, and AMD accepts, a non-exclusive, irrevocable, perpetual, worldwide, transferable, royalty-free license, with the right to sublicense, under Adopter's intellectual property rights in and to any and all Feedback provided by Adopter to AMD hereunder and incorporated into the OPMA Specification (i) to use, copy, create derivative works of, publicly display, publicly perform, and distribute such Feedback as part of the OPMA Specification; and (ii) to use, copy, create derivative works of, publicly display, publicly perform, distribute, make, have made, sell, have sold, import and otherwise dispose of such Feedback in Compliant Portions, without attribution or reference to source. The licenses granted under this Section 3.2 shall survive any termination of this Agreement.

3.3 <u>Information Exchange Forums</u>. In order to promote widespread adoption of OPMA and facilitate communication among various vendors and suppliers licensed thereto, AMD, may, but is not obligated to, develop or maintain one or more forums for the electronic interchange of information between Adopter, AMD and other Fellow Adopters ("Electronic Forums"). Electronic Forums may include, but are not limited to, users groups, web sites, and mailing lists. One or more of such forums may be dedicated for the purpose of receiving Feedback ("Electronic Feedback Forums"). Access to and use of the Electronic Forums may be restricted and subject to additional terms and conditions provided by AMD. Until such time and to the extent that AMD deems otherwise, all information disclosed in the Electronic Forums shall be considered Confidential Information.

3.4 <u>Exceptions</u>. The obligations of confidentiality set forth in Article 3 of this Agreement shall not apply to information that: (a) was in Adopter's possession without confidentiality restriction prior to disclosure hereunder; (b) has become publicly known through no wrongful act of Adopter; (c) has come into the possession of Adopter without confidentiality restrictions from a third party and such third party is under no obligation to AMD to maintain the confidentiality of such information; (d) was developed by Adopter independently of and without reference to any Confidential Information disclosed by AMD hereunder; or (e) has been approved for release by written authorization of AMD.

3.5 <u>Disclosure to Employees, Third Parties</u>. Adopter shall have obtained the execution of proprietary non-disclosure agreements with its employees having access to Confidential Information, which agreements shall contain obligations at least as restrictive as the restrictions contained herein, and shall diligently enforce such agreements. Prior to its publication by AMD, Adopter may provide a copy of the OPMA Specification and an unsigned copy of this Agreement to a third party only if such third party has executed a written agreement with Adopter that prevents disclosure and unauthorized use of Confidential Information by that third party, and obligates such third party to protect such Confidential Information as set forth in Section 3.1.

3.6 <u>Duration</u>. The obligation of confidentiality will survive any termination of this Agreement and will expire five (5) years following receipt of the Confidential Information.

3.7 <u>Remedies.</u> If Adopter breaches any of its obligations with respect to the non-disclosure or unauthorized use of AMD's Confidential Information, AMD shall be entitled to seek equitable relief to protect its interest therein, including but not limited to injunctive relief, as well as money damages.

### Article 4. Disclaimer of Warranties

4.1 Disclaimer of Warranties. ALL MATERIAL, INFORMATION, AND LICENSES PROVIDED BY AMD AND FELLOW ADOPTERS TO ADOPTER HEREUNDER (INCLUDING. WITHOUT LIMITATION, THE OPMA SPECIFICATION), AND ALL LICENSES PROVIDED BY ADOPTER TO AMD AND FELLOW ADOPTERS HEREUNDER, ARE PROVIDED ON AN "AS IS" BASIS, WITH NO WARRANTIES WHATSOEVER, WHETHER EXPRESS, IMPLIED, STATUTORY, CONTRACTUAL OR OTHERWISE, INCLUDING, BUT NOT LIMITED TO, ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, OR NON-INFRINGEMENT, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION, OR SAMPLE. FURTHERMORE, NO WARRANTY OR REPRESENTATION IS MADE OR IMPLIED RELATIVE TO THE VALIDITY OR ENFORCEABILITY OF ANY PATENT LICENSED HEREUNDER, OR RELATIVE TO FREEDOM FROM INFRINGEMENT OF ANY THIRD PARTY PATENTS.

### Article 5. Exclusion of Damages; Limitations of Liability

5.1 <u>Exclusion of Damages.</u> IN NO EVENT WILL EITHER PARTY OR ITS AFFILIATES BE LIABLE TO THE OTHER OR TO ANY THIRD PARTY FOR ANY INDIRECT, PUNITIVE, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES IN CONNECTION WITH OR ARISING OUT OF THIS AGREEMENT (INCLUDING LOSS OF PROFITS, USE, DATA OR OTHER ECONOMIC ADVANTAGE), HOWEVER IT ARISES, WHETHER FOR BREACH OF THIS AGREEMENT, INCLUDING BREACH OF WARRANTY, OR IN TORT (INCLUDING NEGLIGENCE), EVEN IF THAT PARTY HAS BEEN PREVIOUSLY ADVISED OF THE POSSIBILITY OF SUCH DAMAGE. <u>The foregoing shall not apply, however, to waive any</u> remedy otherwise available to AMD for injury suffered or to be suffered by AMD as a result of Adopter's breach of Article 3 of this Agreement.

Limitation of Liability of AMD. IF, AT ANY TIME, AMD OR ANY OF ITS AFFILIATES 5.2 SHALL HAVE ANY LIABILITY ARISING FROM OR BY VIRTUE OF THIS AGREEMENT, AND THE PROVISIONS FOR EXCLUSION OF DAMAGES UNDER SECTION 5.1 OF THIS AGREEMENT DO NOT APPLY, AND WHETHER SUCH LIABILITY IS DUE TO AMD'S OR ITS AFFILIATE'S NEGLIGENCE, BREACH OF ITS OBLIGATIONS UNDER THIS AGREEMENT, OR OTHERWISE, ADOPTER AGREES THAT IN NO EVENT WILL THE TOTAL AGGREGATE LIABILITY OF AMD AND ITS AFFILIATES FOR ANY CLAIMS, LOSSES, OR DAMAGES INCURRED BY ADOPTER OR ANY FELLOW ADOPTER EXCEED \$1,000. THIS LIMITATION OF LIABILITY IS COMPLETE AND EXCLUSIVE, SHALL APPLY EVEN IF AMD OR ITS AFFILIATES HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH POTENTIAL CLAIMS, LOSSES, OR DAMAGES, AND SHALL APPLY REGARDLESS OF THE SUCCESS OR EFFECTIVENESS OF ANY OTHER REMEDIES POSSESSED BY ADOPTER, ITS CUSTOMERS, OR ANY THIRD PARTIES. THIS LIMITATION OF LIABILITY REFLECTS AN AGREED ALLOCATION OF RISK BETWEEN AMD AND ADOPTER IN VIEW OF THE NATURE OF THIS TRANSACTION.

### Article 6. Termination

6.1 <u>Term</u>. This Agreement shall commence upon the Effective Date, and shall continue until terminated as provided herein.

6.2 <u>Termination By Adopter</u>. Adopter may terminate this Agreement at any time upon giving AMD written notice of termination. Termination under this Section 6.2 shall be effective as of the date that AMD receives such written notice of termination from Adopter. After the effective date of termination, the licenses granted by Adopter to AMD under Sections 1.2 and 3.2 shall terminate, except as provided in Section 6.4 below or elsewhere in this Agreement.

6.3 <u>Termination By AMD</u>. AMD may terminate this Agreement upon providing Adopter with written notice of termination if Adopter is in material breach of this Agreement and Adopter fails to cure such breach within thirty (30) days after receiving notice to Adopter of such breach and AMD's intention to terminate. After the effective date of termination, the license granted by AMD under Section 1.2 shall terminate, except as provided in Section 6.4 of this Agreement.

6.4 <u>Effect of Termination</u>. Notwithstanding termination of this Agreement by either party for any reason, and subject to the limitations set forth in Section 1.3, the parties acknowledge that the licenses granted under Sections 1.2 and 3.2 shall remain in full force and effect: (a) for the version of the OPMA Specification set forth in Exhibit A and any versions of the OPMA Specification published by AMD more than sixty (60) days prior to the effective date of termination and (b) for any Feedback provided by Adopter prior to the effective date of termination.

6.5 <u>Survival.</u> All rights and obligations of the parties hereunder shall cease upon termination or expiration of this Agreement, except as provided in Section 6.4, and except the obligations in Articles 3, 4, 5, 6 and 7, which shall survive any termination or expiration of this Agreement. No termination, other than a termination for cause, shall relieve either party from the performance of any of its responsibilities or obligations that should have been performed prior to such termination.

### Article 7. Miscellaneous

7.1 <u>Governing Law; Jurisdiction; Venue</u>. The laws of the State of California will govern this Agreement without reference to conflicts of law principles. Jurisdiction and venue for all disputes relating to this Agreement shall lie with the state and federal courts located in Santa Clara County, California.

7.2 <u>No Obligation to Enforce.</u> Nothing contained in this Agreement shall be construed as imposing on either party any obligation to institute any suit or action for infringement of any of its intellectual property rights, or to defend any suit or action brought by a third party which challenges or concerns the validity of any of its intellectual property rights licensed under this Agreement, or to file any patent application or to secure any patent or maintain any patent in force.

7.3 <u>Press Release</u>. AMD may issue press releases regarding the parties' relationship and the nature of this Agreement with Adopter's prior written approval, which shall not be unreasonably withheld, at any time following the execution of this Agreement.

7.4 <u>Compliance With Export Laws.</u> The parties each agree to comply with all U.S. export laws in connection with the marketing, sale and distribution of products licensed from the other party hereunder, including without limitation the Export Administration Regulations administered by the U.S. Department of Commerce and the International Traffic in Arm Regulations administered by the U.S. Department of State.

7.5 <u>No Support</u>. Adopter acknowledges and agrees that other than providing Adopter with the OPMA Specification, AMD is under no obligation to provide additional materials or support to Adopter.

7.6 <u>Relationship of the Parties</u>. The parties are independent contractors under this Agreement and no other relationship is intended, including a partnership, franchise, joint venture, agency, employer/employee, fiduciary, master/servant relationship, or other special relationship. Neither party shall act in a manner that expresses or implies a relationship other than that of independent contractor, nor bind the other party.

7.7 <u>Notices.</u> Unless otherwise provided herein, all notices which shall be given by either party under the provisions of this Agreement shall be in writing and be hand delivered, sent by facsimile transmission followed with written confirmation by mail, sent by commercial overnight delivery, or sent by certified U.S. mail (return receipt requested). Notices shall be deemed given on the date of actual receipt (or refusal of delivery) when hand delivered, upon confirmed transmission when sent by facsimile, one day after having been sent when sent by certified U.S. mail. Notwithstanding anything to the contrary in this Section 7.7, any written notice will be effective no later than the date actually received. Notices shall be addressed as set forth in the signature page hereto.

7.8 <u>Notice of Publication</u>. AMD shall, at its sole discretion, provide Adopter with notice of publication for each future version of the OPMA Specification. Such notice may be sent to Adopter at the address, and in the manner, described in Section 7.7. Alternatively, AMD may provide email notification of publication to Adopter at the email address provided on the signature page hereto.

7.9 <u>Entire Agreement; Amendment</u>. This Agreement (including any attached exhibits) constitutes the final and entire agreement between the parties, and supercedes all prior written and oral agreements, understandings, or communications with respect to the subject matter of this Agreement (including without limitation any memorandums of understanding, written proposals, and term sheets). Notwithstanding the foregoing, nothing in this Agreement shall be deemed to limit the scope of any license granted in any prior agreement executed between the parties that is of a broader scope than the licenses granted hereunder. This Agreement may not be modified except in writing signed by a duly authorized representative of each party. It is expressly understood and agreed that no employee, agent, or other representative of AMD has any authority to bind AMD with respect to any statement, representations, warranty, or other expression unless the same is specifically set forth in this Agreement. It is also understood and agreed that no usage of trade or other regular practice or method of dealing between the parties

hereto shall be used to modify, interpret, supplement, or alter in any manner the terms of this Agreement.

7.10 <u>No Waiver</u>. The waiver by either party of any breach of any provision of this Agreement shall not operate or be construed as a waiver of any other or a subsequent breach of the same or a different provision.

7.11 <u>Assignment</u>. Neither party shall assign, transfer, or otherwise delegate any of its rights, duties, or obligations under this Agreement in whole or in part to any individual, firm or corporation without the prior written consent of the other party, which consent shall not be unreasonably withheld; provided however, that (a) AMD may assign this Agreement, in whole or in part, to one or more of its Affiliates or (b) AMD may assign this Agreement to a trade association or similar entity. Any attempt to assign, transfer or otherwise delegate any of the rights, duties, or obligations under this Agreement without the prior written consent of the other party shall be void. Notwithstanding the foregoing, either party may assign its rights, duties, and obligations hereunder without approval of the other party to a party that succeeds to all or substantially all of its assets (whether by sale, merger, operation of law or otherwise), provided that such assignee or transferee agrees in writing to be bound by the terms and conditions of this Agreement. The rights and liabilities of the parties under this Agreement will bind and inure to the benefit of the parties' permitted assigns and successors.

7.12 <u>Captions</u>. The captions appearing in this Agreement have been inserted as a matter of convenience and in no way define, limit or enlarge the scope of this Agreement or any of the Sections thereto.

7.13 <u>Severability</u>. In the event that any one or more of the provisions of this Agreement is determined by a court of competent jurisdiction to be invalid, unenforceable or illegal, such invalidity, unenforceability or illegality shall not affect any other provisions of this Agreement, and the Agreement shall be construed as if the challenged provision had never been contained herein. The parties further agree that in the event such provision is an essential part of this Agreement, they will immediately begin negotiations for a suitable replacement provision.

7.14 <u>Force Majeure</u>. Neither party will be deemed in default of this Agreement to the extent that performance of its obligations or attempts to cure any breach are delayed or prevented by reason of any act of God, fire, natural disaster, accident, act of government, shortages of material or supplies or any other cause beyond the control of such party, provided that such party gives the other party written notice thereof promptly and, in any event, within thirty (30) days of discovery thereof and uses good faith efforts to so perform or cure. In the event of such a Force Majeure, the time for performance or cure will be extended for a period equal to the duration of the Force Majeure but not in excess of six (6) months.

7.15 <u>Binding</u>. This Agreement shall be binding on the parties, their Affiliates, subsidiaries, successors, and assigns (if any), and they each warrant that the signatories hereto are authorized to execute this Agreement on behalf of the respective party.

7.16 <u>No Bias</u>. This Agreement shall be interpreted as written and negotiated jointly by the parties. It shall not be strictly construed against either party, regardless of the actual drafter of the Agreement.

7.17 <u>Costs, Attorneys' Fees, and Experts' Fees</u>. In the event any obligation of this Agreement must be enforced, through litigation or otherwise, the prevailing party will be entitled to recover reasonable costs and expenses incurred in enforcing the obligation, including costs, reasonable attorneys' fees and experts' fees.

7.18 <u>Counterparts and Facsimile</u>. This Agreement may be executed in duplicate and either copy or both copies are considered originals, but all of which together constitute one and the same instrument. This Agreement may be executed by facsimile signature.

7.19 <u>Expenses</u>. Each of the parties shall bear its own costs and expenses incurred hereunder, including, without limitation, travel, employee compensation, and incidental expenses.

### Article 8. Glossary

8.1 **"Affiliate"** means an entity that directly or indirectly Controls or is Controlled by, or is under common Control with another entity, so long as such Control exists. For purposes of this Section 8.1, "Control" means control or ownership of (a) more than fifty percent (50%) of an entity's outstanding shares or stock entitled to vote for the election of directors or similar managing authority of that entity, or (b) in the case of an entity not having outstanding shares or securities, more than fifty (50%) of the right to make the decisions for that entity.

8.2 **"Compliant Portion"** means only those specific portions of products (hardware, software or combinations thereof) that: (a) implement and are compliant with all relevant portions of an OPMA Specification, and (b) are within the bounds of the Scope.

8.3 **"Feedback**" has the meaning given in Section 3.2 of this Agreement.

8.4 **"OPMA"** means the electrical, mechanical, and firmware interfaces as described in the OPMA Specification.

8.5 **"OPMA Specification"** means the specification attached hereto as Exhibit A setting forth the description and requirements (including, but not limited to, logical and electrical specifications) for OPMA, and any future version of such specification published by AMD under the title "Open Platform Management Architecture Specification."

8.6 **"Necessary Claims"** of a party means those claims of all patents and patent applications throughout the world to which such party or its Affiliates has the right at any time during the term of this Agreement to grant licenses without such grant resulting in payment of royalties or other consideration to third parties (except for payments to Affiliates or employees), which claims are (a) necessarily infringed by an implementation of the OPMA Specification and (b) within the bounds of the Scope. Necessary Claims do not include any claims other than those set forth above even if contained in the same patent as Necessary Claims.

8.7 **"Scope"** means the protocols, electrical signaling characteristics, commands, and clocking signals solely to the extent disclosed with particularity in the OPMA Specification where the sole purpose of such disclosure is to enable products to interoperate, interconnect, or communicate as defined within the OPMA Specification. Notwithstanding the foregoing, the Scope shall not include (a) any enabling technologies that may be necessary to make or use any product or portion thereof that complies with the OPMA Specification, but are not themselves expressly set forth in the OPMA Specification (e.g., semiconductor manufacturing technology, X86 architecture, and processor microarchitecture); and (b) the implementation of other published specifications not developed by or for AMD but referred to in the body of the OPMA Specification.

Executed by the undersigned authorized representatives of AMD and Adopter, respectively, to be effective as of the Effective Date.

Adopter Company Name

Signature

Representative Name (Printed)

Title

Date

Advanced Micro Devices, Inc.

Brian Spross AMD Senior Technology Counsel

Date

### AMD Address for Legal Notice:

Advanced Micro Devices, Inc. 5204 E. Ben White Blvd., M/S 562 Austin, Texas 78741 ATTENTION: CPG Legal Facsimile: 512-602-4932

### AMD Technical Contact:

Dave Tobias 800-538-8450 E-Mail: dave.tobias@amd.com

### Adopter Address for Legal Notice:

\_\_\_\_\_

Facsimile:

### Adopter Technical Contact:

Name: \_\_\_\_\_\_ Phone: \_\_\_\_\_\_ E-Mail: \_\_\_\_\_\_

Adopter: Please have an authorized representative sign on behalf of Adopter and fax the Agreement to AMD Legal, Attention: Sarah Blankenship, Fax No. 512-602-4932. AMD Legal will return a counter-signed Agreement to Adopter's Legal contact as listed above.

Publication #32200Revision:1.3Issue Date:January 2008

#### © 2004–2008 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. The information contained herein may be of a preliminary or advance nature and is subject to change without notice. No license, whether express, implied, arising by estoppel, or otherwise, to any intellectual property rights are granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### Trademarks

AMD, the AMD Arrow logo, AMD Opteron, and combinations thereof are trademarks of Advanced Micro Devices, Inc.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

32200 Rev. 1.3 January 2008

**Open Platform Management Architecture Specification**

## Contents

| Revision | History                                                | 10 |

|----------|--------------------------------------------------------|----|

| Chapter  | 1 Introduction                                         | 11 |

| 1.1      | Overview of OPMA Goals                                 | 11 |

| 1.2      | Background                                             | 11 |

| 1.3      | Basic Goals for OPMA                                   | 12 |

| 1.4      | Audience and Purpose of Document                       | 13 |

| 1.5      | Acronyms and Terminology                               | 13 |

| 1.6      | Conventions                                            | 17 |

| 1.7      | Reference Documents                                    | 18 |

| Chapter  | 2 OPMA Functionality Tiers                             | 19 |

| 2.1      | M1—The Value Solution                                  | 19 |

| 2.2      | M2—Reasonable Price, Security and Performance          | 20 |

| 2.3      | M3—High-End Solution with Graphics Console Redirection |    |

| 2.4      | Mx—Upgrade Soldered-Down Management Subsystem          |    |

| Chapter  |                                                        |    |

| 3.1      | Background                                             | 23 |

| 3.2      | Signal Callout Grouped by Functions                    | 23 |

| 3.2.1    | 1 LED Control Signals                                  | 23 |

| 3.2.2    | 2 USB Interface Signals                                | 24 |

| 3.2.3    | 3 Push-Button Signals                                  | 24 |

| 3.2.4    | 4 Video Capture DVI-I Signals                          | 25 |

| 3.2.5    | 5 Multi-Bank Fan Control Signals                       | 26 |

| 3.2.6    | 6 Multiplexed Fan Tach Input Signals                   | 26 |

| 3.2.7    | 7 Fan Tach Mux Bank Selector Signals                   | 26 |

| 3.2.8    | 8 Single Wire Analog Voltage Sensor Signals            | 27 |

| 3.2.9    | 9 MCard Serial Port and ICMB                           | 27 |

| 3.2.1    | 10 Serial Over LAN Feedback Path                       | 28 |

| 3.2.1    | 11 Dedicated Management Ethernet Signals               | 28 |

| 3.2.1    | 12 BMC Host Interface ID Signals                       | 28 |

| 3.2.1    | 13 MCard Presence Detection Signal                     | 29 |

| 3.2.1    | 14 System Status Signals                               | 29 |

| 3.2.1   | 5 System Control Signals                                                 |    |

|---------|--------------------------------------------------------------------------|----|

| 3.2.1   | 6 I <sup>2</sup> C or SMBus Signals                                      |    |

| 3.2.1   | 7 LPC Bus Signals                                                        |    |

| 3.2.1   | 8 Miscellaneous Signals                                                  |    |

| 3.2.1   | 9 Firmware Debugger Probe Signals                                        |    |

| 3.2.2   |                                                                          |    |

| 3.3     | OPMA Hardware Resources                                                  |    |

| 3.3.1   | SEEPROM Address Reservation                                              |    |

| 3.3.2   | 2 I <sup>2</sup> C or SMBus Multiplexer Address Reservation              |    |

| 3.3.3   | 6                                                                        |    |

| 3.4     | OPMA Feature Card Power Requirements                                     |    |

| 3.5     | OPMA Feature Card Signal Tolerance Requirements                          |    |

| 3.6     | OPMA Signals Grouped by Function                                         |    |

| Chapter | 4 OPMA Connector Specification and Pin Assignments                       | 41 |

| Chapter | 5 OPMA Feature Card Mechanicals                                          | 45 |

| 5.1     | Board Mechanical Outline                                                 | 45 |

| 5.2     | Mechanical Strategy and Configuration                                    |    |

| 5.3     | OPMA LAN and Serial Port Connector Scheme                                |    |

| Chapter | 6 OPMA SoL Support                                                       | 51 |

| Chapter | 7 Specification Version Compatibility Rules                              | 61 |

| 7.1     | Electrical Compatibility                                                 | 61 |

| 7.2     | Backward Compatibility                                                   | 61 |

| 7.3     | Forward Compatibility                                                    |    |

| 7.4     | Compatibility for Transition from MCARD_I <sup>2</sup> C_SIDEBAND_NIC to |    |

|         | MCARD_I <sup>2</sup> C_CPU Bus                                           |    |

| Chapter | 8 Motherboard Hardware Support for OPMA Compliance                       | 63 |

| 8.1     | General Signal Termination                                               | 63 |

| 8.2     | MCard SMI Generation Support                                             | 63 |

| 8.3     | Fan Tachometer Read Back                                                 |    |

| 8.4     | Fan Speed Control                                                        | 64 |

| 8.5     | Clear CMOS Circuit                                                       | 66 |

| 8.6     | System Speaker Control Circuit                                           | 67 |

| 8.7     | Local Access Lock Out                                                    | 67 |

| 8.8     | ACPI State Reporting                                       |    |

|---------|------------------------------------------------------------|----|

| 8.9     | DVI–Digital Visual Interface                               | 69 |

| 8.10    | Firmware Debug Header                                      | 69 |

| 8.11    | ICMB RS-485 Level Translation Circuit                      | 70 |

| 8.12    | Management UART Signal Level Translation                   | 70 |

| 8.13    | Management UART Signal Multiplexing                        | 70 |

| 8.14    | Support for Dedicated Management LAN                       | 71 |

| 8.15    | MCard Presence Detect and Interface ID Support             | 71 |

| 8.16    | Motherboard Support for I/O Functions                      | 71 |

| 8.17    | Motherboard Support for mCard SCI Interrupt Signal         | 72 |

| 8.18    | Motherboard I/O Terminations                               | 72 |

| 8.19    | Motherboard Support for NC-SI                              | 72 |

| 8.20    | Motherboard Support for MCARD_I2C_CPU Bus                  | 72 |

| Chapter | • 9 OPMA Host System BIOS Support                          | 73 |

| 9.1     | MCard Presence Detect                                      | 73 |

| 9.2     | MCard IPMI Command Interface Type Detection                | 73 |

| 9.3     | IPMI Command Hardware Interface Support                    | 74 |

| 9.4     | IPMI Command BIOS Interface Support                        | 75 |

| 9.5     | MCard Presence, Health and BMC Firmware Revision Reporting | 75 |

| 9.6     | System Identification                                      | 76 |

| Chapter | 10 OPMA Feature Card Considerations                        | 77 |

| 10.1    | Interface Identification                                   | 77 |

| 10.2    | CMOS Reset                                                 | 77 |

| 10.3    | Respect the Reserved Signals                               | 78 |

| 10.4    | Sideband Signals                                           | 78 |

| 10.5    | Local Voltages                                             | 78 |

| 10.6    | Fan Tachometer Multiplexing                                |    |

| 10.7    | Single Back Panel Serial Connector Support                 | 78 |

| 10.8    | I <sup>2</sup> C or SMBus Mux Addressing                   |    |

| Chapter | 11 BMC Firmware OPMA Compatibility Requirements            | 79 |

| 11.1    | KCS Interface                                              | 79 |

| 11.2    | MCard IPMI Interface ID GPIO Initialization                | 79 |

### **Contents**

###

| Open Platfo | orm Management Architecture Specification 3220    | 0 Rev. 1.3 | January 2008 |

|-------------|---------------------------------------------------|------------|--------------|

| 11.3 MC     | Card-Specific IPMI-OEM Command Support            |            |              |

| 11.4 Sys    | stem Identification and mCard Capabilities        |            |              |

| 11.5 Ho     | st System Compatibility Detection and Handling    |            |              |

| 11.6 Up     | grade Kit Support                                 |            |              |

| -           | Itiple Sensor Mapping Support                     |            |              |

|             | PI State Detection                                |            |              |

| 11.9 Fai    | n Monitoring                                      |            |              |

|             | n Control                                         |            |              |

| 11.11 Mu    | Ilti-Master I <sup>2</sup> C or SMBus Support     |            |              |

| Chapter 12  | OPMA-Defined IPMI Command Extensions              |            |              |

| 12.1 Set    | /Get Sensor Reading Offset Command                |            |              |

| 12.1.1      | Command—SetSensorReadingOffset                    |            |              |

| 12.1.2      | Command—GetSensorReadingOffset                    |            |              |

| 12.2 Set    | /Get System Type Identifier                       |            |              |

| 12.2.1      | System ID                                         |            |              |

| 12.2.2      | Command—SetSystemTypeIdentifier (cmd A0h)         |            |              |

| 12.2.3      | Command—GetSystemTypeIdentifier (cmd A1h)         |            | 89           |

| 12.3 MC     | Card Capabilities Identifier                      |            |              |

| 12.3.1      | Command—GetmCardCapabilities                      |            |              |

| 12.4 MC     | Card Clear CMOS                                   |            |              |

| 12.4.1      | Command—ClearCMOS (cmd A3h)                       |            |              |

| 12.5 MC     | Card Local Lock Out                               |            |              |

| 12.5.1      | Command—SetLocalLockOutState (cmd A4h)            |            |              |

| 12.5.2      | Command—GetLocalLockOutState (cmd A5h)            |            |              |

| 12.6 Ge     | t Supported Host System IDs                       |            |              |

| 12.6.1      | Command—GetSupportedHostIDs (cmd A6h)             |            |              |

| 12.7 Re     | quired Support of Normally Optional IPMI Commands |            |              |

| 12.7.1      | Set/GetSensorThreshold Commands                   |            |              |

| 12.7.2      | GetSensorReadingFactors Command                   |            |              |

| Appendix A  | Boot Sequence Theory of Operation                 |            | 101          |

| Appendix B  | IPMI OEM Commands Summary                         |            |              |

| Appendix C  | Specification Modification Roadmap                |            |              |

## **List of Figures**

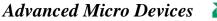

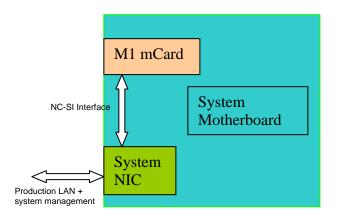

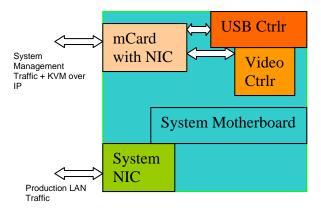

| Figure 1. M1 mCard with NC-SI Shared NIC Configuration2                        | 20             |

|--------------------------------------------------------------------------------|----------------|

| Figure 2. M2 mCard with Dedicated NIC                                          | 20             |

| Figure 3. M3 with Dedicated NIC and KVMoIP Configuration                       | 21             |

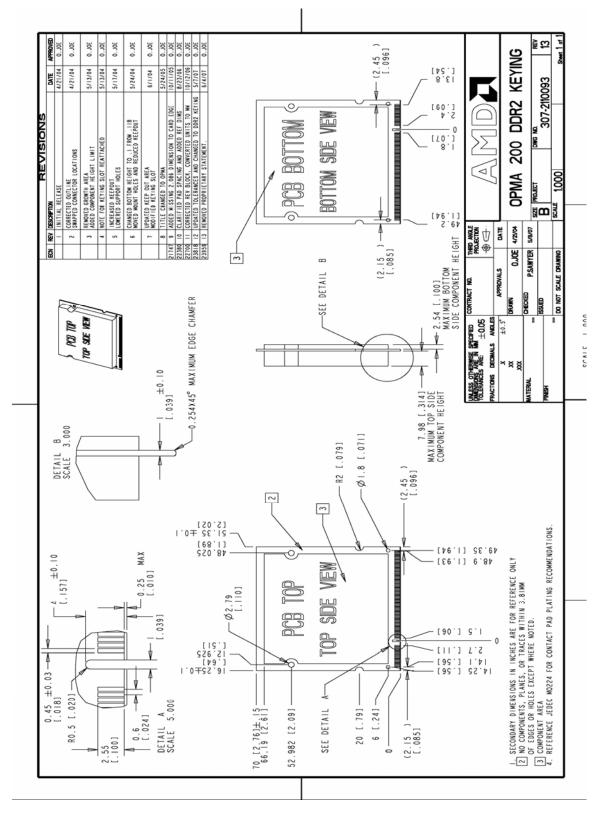

| Figure 4. MCard Mechanical Form Factor4                                        | <b>1</b> 7     |

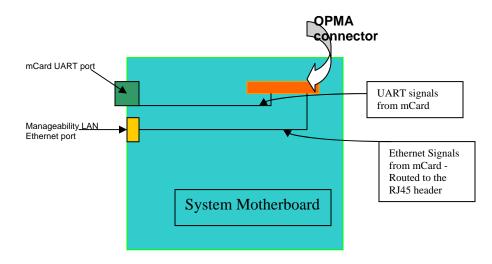

| Figure 5. Management LAN and UART Connectors for an mCard4                     | <del>1</del> 9 |

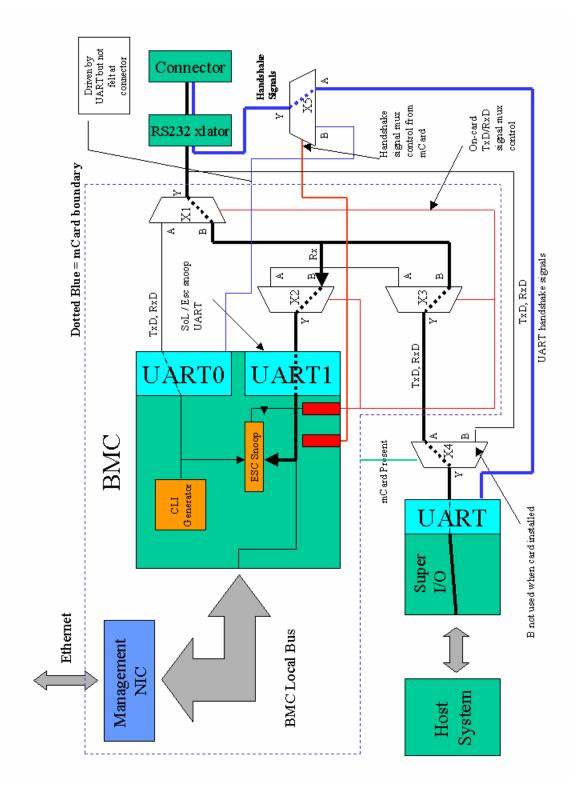

| Figure 6. Device B mCard with Host UART Connected to Serial Port Connector (A) | 54             |

| Figure 7. Device B mCard with Host UART Connected to Serial Port Connector (B) | 55             |

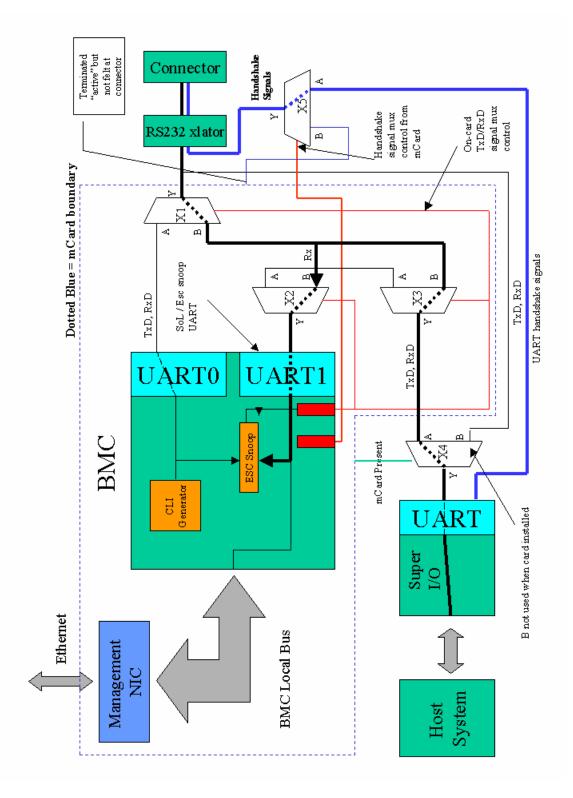

| Figure 8. Device B Representative mCard in SoL Mode (A)                        | 56             |

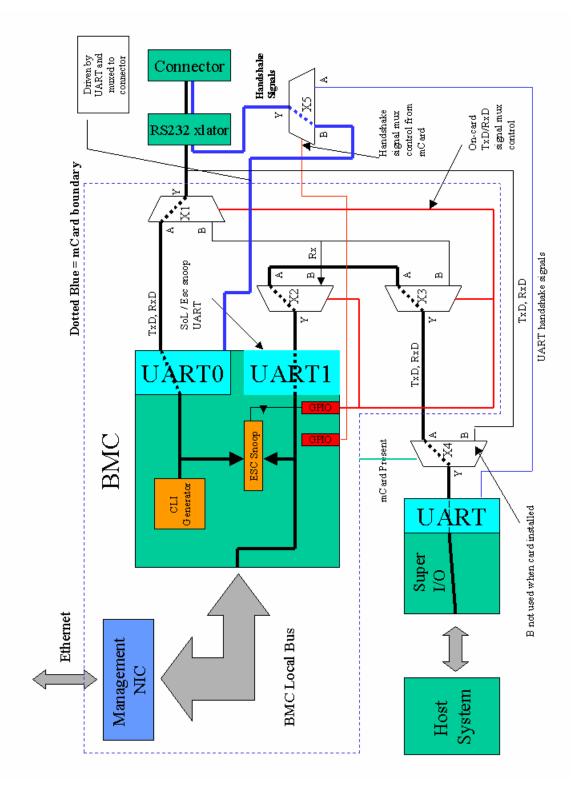

| Figure 9. Device B Representative mCard in SoL Mode (B)                        | 57             |

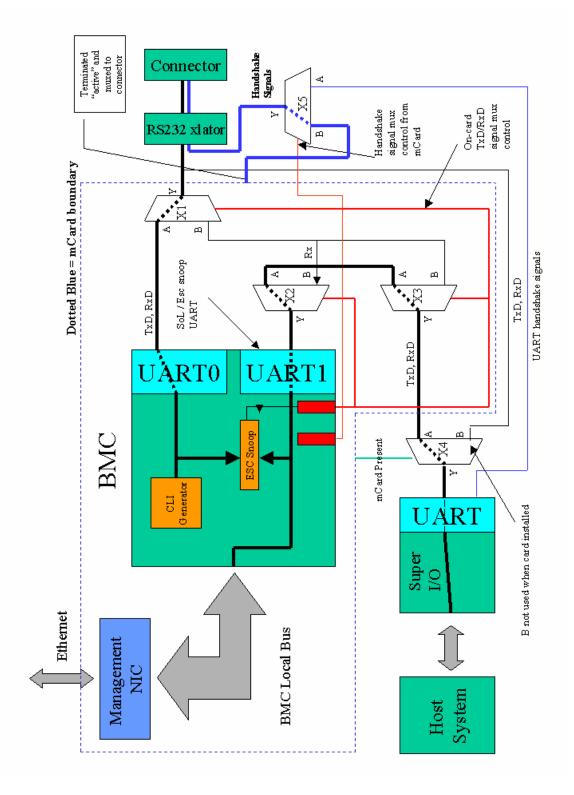

| Figure 10. Device A Representative mCard in Both CLI and SoL Modes             | 58             |

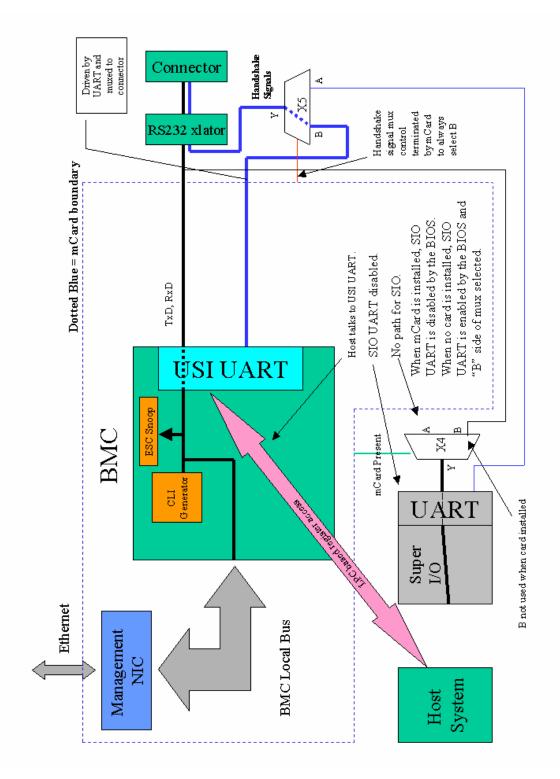

| Figure 11. Host Serial Port Operation with No mCard Installed                  | 59             |

| Figure 12. Fan Tach Monitoring Circuit Logic Block Diagram $\epsilon$          | 54             |

| Figure 13. Fan Tach Monitoring Circuit Example $\epsilon$                      | 54             |

| Figure 14. Fan Speed Control Circuit Logic Block Diagram $\epsilon$            | 55             |

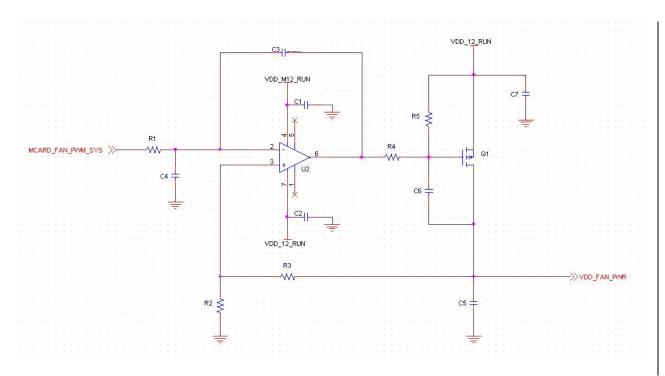

| Figure 15. Fan Speed Control PWM-to-DC Converter Circuit Example $\epsilon$    | 55             |

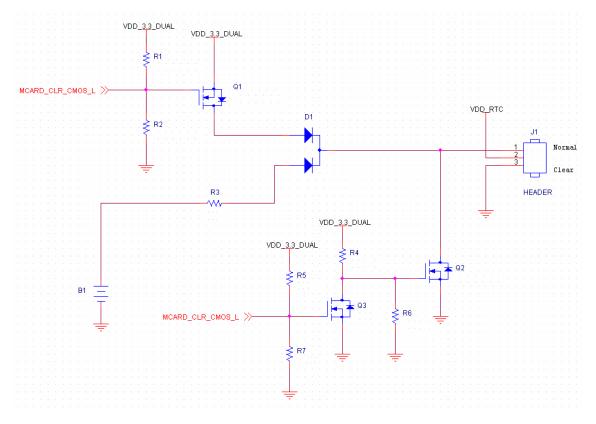

| Figure 16. CMOS Clearing Circuit Example with MCARD_CLR_CMOS_L Signal $\dots$  | 56             |

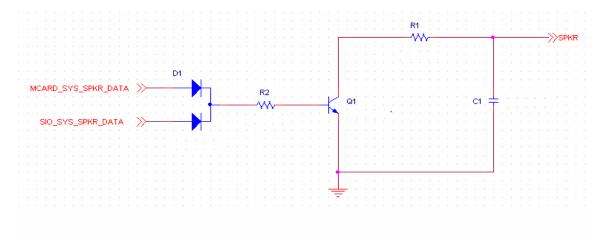

| Figure 17. Speaker Control Circuit Example $\epsilon$                          | 57             |

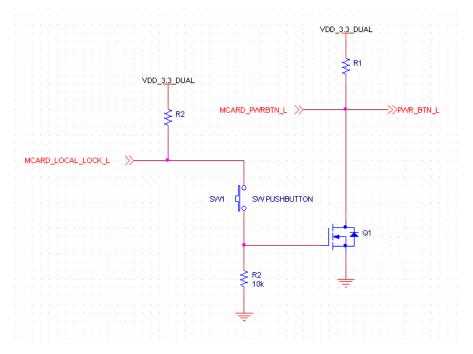

| Figure 18. Partial Circuit Example for Local Access Lock Out $\epsilon$        | 58             |

| Figure 19. Motherboard Berg Header Numbering Scheme (Top View)                 | 59             |

###

**Open Platform Management Architecture Specification**

## **List of Tables**

| Table 1. Acronyms and Terminology                              | . 13 |

|----------------------------------------------------------------|------|

| Table 2. Conventions                                           | . 17 |

| Table 3. Reference Documents                                   | . 18 |

| Table 4. Network Controller Sideband Interface (NC-SI) Signals | . 34 |

| Table 5. OPMA Signals                                          | . 37 |

| Table 6. Pin Assignments for the OPMA Connector                | . 41 |

| Table 7. Signal Encoding for ACPI State Reporting              | . 68 |

| Table 8. Debug Header-to-OPMA Connector Mapping                | . 69 |

| Table 9. Card Detect Signal States                             | . 73 |

| Table 10. Management Subsystem Host Interface Type Encoding    | . 74 |

| Table 11. Set/GetSensorReadingOffset NetFn Codes               | . 84 |

| Table 12. SetSensorReadingOffset Command Format                | . 84 |

| Table 13. SetSensorReadingOffset Completion Codes              | . 85 |

| Table 14. GetSensorReadingOffset Command Format                | . 85 |

| Table 15. GetSensorReadingOffset Completion Codes              | . 86 |

| Table 16. Set/GetSystemTypeIdentifier NetFn Codes              | . 87 |

| Table 17. SetSystemTypeIdentifier Command Format               | . 88 |

| Table 18. SetSystemTypeIdentifier Completion Codes             | . 89 |

| Table 19. GetSystemTypeIdentifier Command Format               | . 89 |

| Table 20. GetSystemTypeIdentifier Completion Codes             | . 90 |

| Table 21. GetmCardCapabilities NetFn Code                      | . 91 |

| Table 22. GetmCardCapabilities Command Format                  | . 91 |

| Table 23. GetmCardCapabilities Completion Codes                | . 93 |

| Table 24. ClearCMOS NetFn Codes                                | . 94 |

| Table 25. ClearCMOS Control Command Format                     | . 94 |

| Table 26. ClearCMOS Completion Code                            | . 95 |

| Table 27. Set/GetLocalAccessLockOutState NetFn Code            | . 95 |

| Table 28. SetLocalLockOutState Command Format                  | . 95 |

| Table 29. SetLocalLockOutState Completion Codes                | . 96 |

| Table 30. GetLocalLockOutState Command Format                  | . 96 |

| 32200 | Rev. 1 | .3 | January | 2008 |

|-------|--------|----|---------|------|

|       |        |    |         |      |

| Table 31. GetLocalLockOutState Completion Codes | 97  |

|-------------------------------------------------|-----|

| Table 32. GetSupportedHostIDs NetFn Codes       | 97  |

| Table 33. GetSupportedHostIDs Command Format    | 98  |

| Table 34. GetSupportedHostIDs Completion Codes  | 99  |

| Table 35. IPMI OEM Commands                     | 104 |

## **Revision History**

Revision bars indicate changes from the last revision.

| Date          | Revision | Description                                                                                                                                                                                                                                                                                                                             |

|---------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| January 2008  | 1.3      | Added Network Controller Sideband Interface (NC-SI) support to the specification. Introduced CPU interface I <sup>2</sup> C/SMBus. Provided additional clarifications in other sections.                                                                                                                                                |

| June 2007     | 1.2      | Updated mechanical connector specification to reflect SO-DIMM DDR2 only.                                                                                                                                                                                                                                                                |

| May 2006      | 1.1      | Clarifications to SO-DIMM connector keying and mechanical drawing, mCard power consumption, PCI reset signal, SEEPROM and I <sup>2</sup> C/SMBus device addressing, motherboard I/O terminations, firmware debug header and fan types sections. Added Appendix D. <i>Technical Implications of Changes in OPMA Specification R 1.1.</i> |

| May 2005      | 1.02     | Updates to fan mux select signal polarity (pages 26, 37, and 42).                                                                                                                                                                                                                                                                       |

| February 2005 | 1.01     | Removed Appendix D.                                                                                                                                                                                                                                                                                                                     |

| December 2004 | 1.00     | Initial public release.                                                                                                                                                                                                                                                                                                                 |

## Chapter 1 Introduction

This chapter describes the Open Platform Management Architecture (OPMA) goals and background information.

## 1.1 Overview of OPMA Goals

### OPMA:

- describes the motherboard and subsystem card aspects of a modular manageability architecture for servers and workstations and explains the benefits of this approach. Management subsystems feature cards that are OPMA compliant, which are known as *mCards*.

- describes three tiers of mCard functionality that drive three different price ranges for mCards. These feature tiers are provided as examples; the market decides what feature sets are actually offered in the OPMA-defined mCard form factor both initially and over time. The example tiers were chosen to show the range of manageability solutions that were considered in the definition of the OPMA hardware interface, required hardware resources, and firmware extensions.

- provides a publicly available specification for a manageability subsystem electrical interface, mechanical form factor, and firmware interfaces for creating OPMA-compliant motherboards and OPMA feature cards (mCards) for each of the described functionality tiers.

## 1.2 Background

In the past, platform hardware manageability in servers was treated as a premium, OEM-specific value-added feature. As the marketplace matures, hardware management is evolving into a standards-based, "must have" feature found on the vast majority of enterprise class servers. Today, the BMC (Baseboard Management Controller) firmware and IPMI (Intelligent Platform Management Interface) command interfaces to the host and remote systems are clearly defined and widely accepted.

Despite the advances made in standardizing manageability firmware and software interfaces, manageability hardware subsystems are still proprietary and are often soldered to the baseboard. Because of this practice, manageability hardware subsystems:

- are reinvented for many server platforms, often times even within a given server motherboard/system manufacturer's product lines.

- may be inefficient to develop due to lack of re-use across designs, thus adding significantly to time to market, system development costs and risk.

- may not provide the proper flexibility of cost/benefit trade-offs for the server customer.

- may not provide a customer driven, cost-effective upgrade path for servers as manageability requirements change.

• do not enable the building of an efficient, competition-based infrastructure ecosystem for hardware manageability.

To address these issues, AMD has developed the OPMA specification.

## **1.3 Basic Goals for OPMA**

As server volumes rise, server prices fall. All areas of server design must be more closely scrutinized for efficiency that drives cost savings while retaining or increasing customer value, features, and flexibility. Industry standards bodies have made good strides in standardizing the external command interfaces to the management subsystem. OPMA extends the standardization concept to the management subsystem hardware interconnect and associated system architecture. The combination of a standardized external command interface with standardized, modular management subsystem architecture (OPMA) forms the basis of efficient, cost effective management subsystems. OPMA is primarily oriented at standardizing hardware interfaces. OPMA does not preclude the use of external command interfaces other than IPMI.

OPMA does not dictate a management subsystem feature set. Instead, it provides a robust hardware interface that allows management subsystems to be attached to server motherboards in a standardized way. The main goals of the OPMA specification are to:

- standardize the server management subsystem hardware interface architecture using a modular approach while continuing to allow intelligent innovation in management subsystems.

- reduce platform development risk, cost, and time to market.

- broaden motherboard applicability. Avoid missed system sales due to the management subsystem not meeting the customers' needs or cost targets.

- enable the evolution of manageability subsystem hardware into a COTS (commercial off the shelf) model that supports various tiers of capability/price.

- assist OEMs in moving to an outsourcing model for server design by enabling a multi-vendor approach for supplying the manageability subsystem. Give OEMs a build or buy decision that is not available today.

- increase customer satisfaction by providing more customer flexibility and choice at a reduced cost.

- enable cost reductions obtained by using COTS devices to drive enhanced manageability into markets that could not previously afford it.

- enable management subsystem infrastructure competition by providing a level playing field.

- free up the PCI slot commonly used for Keyboard, Video, and Mouse over Internet Protocol (KVMoIP) feature cards while increasing performance of the remote graphics console.

- achieve all of the above with minimal impact on BMC and BIOS firmware investments.

### **1.4** Audience and Purpose of Document

This document is the single point of OPMA architecture definition. The audience is management, marketing, and engineering personnel of ISVs, IHVs, ODMs and OEMs who develop, test, and market server platforms and management subsystems.

## **1.5** Acronyms and Terminology

Table 1 lists the definitions of acronyms and terms used in this specification. In some of the definitions, the IPMI specification is referred to. For detailed information on the IPMI specification and other referenced specifications, refer to Table 3 on page 18.

| Term             | Definition                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACPI             | Advanced Configuration and Power Interface. See ACPI specification for details.                                                                                                                                                                                                                                                                                                       |

| BIOS             | Basic Input Output System. This is the boot firmware on a standard PC system (including servers). It also provides some abstraction for system hardware.                                                                                                                                                                                                                              |

| BMC              | Baseboard Management Controller. This is the main component of the OPMA subsystem that provides IPMI command processing, alerting, error logging, etc. in compliance with the IPMI specification.                                                                                                                                                                                     |

| BT               | IPMI's Block Transfer command interface.                                                                                                                                                                                                                                                                                                                                              |

| CLI              | Command Line Interface. This is a text-based interface to a BMC.                                                                                                                                                                                                                                                                                                                      |

| CMOS             | Complimentary-symmetry Metal Oxide Semiconductor. This term in this document refers to a battery-backed storage element found on legacy PC systems.                                                                                                                                                                                                                                   |

| COTS             | Commercial Off The Shelf. This refers to items that are commonly available commercially, not custom and not military.                                                                                                                                                                                                                                                                 |

| DDC              | Display Data Channel. Provides plug-and-play data to whatever device the monitor is plugged into.                                                                                                                                                                                                                                                                                     |

| DDWG             | Digital Display Working Group—owns DVI specification.                                                                                                                                                                                                                                                                                                                                 |

| DMTF             | Distributed Management Task Force – www.dmtf.org                                                                                                                                                                                                                                                                                                                                      |

| DVI              | Digital Visual Interface. A set of buses for moving video data within a system. DVI-D digitally encodes the video data and then puts it out onto a bus. DVI-A is simply the same analog video signals seen on a standard VGA connector. DVI-I is the union of DVI-D and DVI-A signals to provide both methods of video information transmission over a single cable and/or connector. |

| FRU              | Field Replaceable Unit. See the IPMI specification for details.                                                                                                                                                                                                                                                                                                                       |

| I <sup>2</sup> C | Inter-Integrated Circuit bus. A simple two-wire bus often used to allow system-<br>processing elements to read low cost sensor devices. An $I^2C$ device interfaces to the<br>system via the $I^2C$ bus.                                                                                                                                                                              |

| ICMB             | Intelligent Chassis Management Bus. An IPMI-defined bus for connecting management processors that exist in separate physical chassis. See the IPMI specification for details.                                                                                                                                                                                                         |

### **Table 1. Acronyms and Terminology**

| Term       | Definition                                                                                                                                                                                                                                                  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IHV        | Independent Hardware Vendor. Used in this specification to refer to the manufacturer of mCard subsystem boards.                                                                                                                                             |

| IPMI       | Intelligent Platform Management Interface specification. See IPMI specification for details.                                                                                                                                                                |

| IPMB       | Intelligent Platform Management Bus. An IPMI-defined bus for connecting management processors that exist in a single physical chassis. See IPMI specification for details.                                                                                  |

| ISV        | Independent Software Vendor. Used in this specification to refer to the manufacturer of OPMA subsystem board firmware, OS-level drivers, and OS-level applications.                                                                                         |

| JTAG       | Joint Test Action Group                                                                                                                                                                                                                                     |

| KCS        | IPMI's Keyboard Controller Style command interface                                                                                                                                                                                                          |

| KVMoIP     | Keyboard, Video, and Mouse over Internet Protocol. Used for implementing remote video consoles on headless (i.e., no local keyboard mouse or display) servers.                                                                                              |

| LCD        | Liquid Crystal Display                                                                                                                                                                                                                                      |

| LED        | Light Emitting Diode                                                                                                                                                                                                                                        |

| LPC        | A reference to the low pin count bus specification. This is a common host system interface bus for BMCs.                                                                                                                                                    |

| LUN        | IPMI Logical Unit Number                                                                                                                                                                                                                                    |

| mCard      | This is the generic name for an OPMA-compliant Management Card. It is a modular, connector based management subsystem which contains the BMC and associated hardware resources. In this document, "mCard" and "OPMA feature card" are used interchangeably. |

| NetFn Code | Net Function value parameter as defined in the IPMI specification document.                                                                                                                                                                                 |

| NIC        | Network Interface Controller (a.k.a Ethernet controller). Typically includes an Ethernet<br>Media Access Controller and may also include an integrated physical layer (PHY).                                                                                |

| NC-SI      | Network Controller Sideband Interface – A sideband NIC interface standard developed<br>by the Distributed Management Task Force (DMTF).                                                                                                                     |

| ODM        | Original Design Manufacturer. Used in this specification to refer to the developers of motherboards that are used in a completed server system.                                                                                                             |

| OEM        | Original Equipment Manufacturer. Used in this specification to refer to the server system manufacturer.                                                                                                                                                     |

| OOB        | Out Of Band. A platform hardware management communications channel that connects a remote console directly to the BMC. This channel is working even when the managed platform is in a soft off state.                                                       |

| Term    | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPMA    | Open Platform Management Architecture. This acronym is used in several contexts as follows:<br>OPMA architecture—This is the overall description of the way OPMA subsystem cards connect to and interact with the motherboard. It includes not only the OPMA connector and associated electrical specification, but required firmware interfaces as well as other resources located on the motherboard that are required to support the intended usage model. The OPMA architecture is described in this specification. |

|         | OPMA subsystem—An implementation of the OPMA architecture on the motherboard taken together with an OPMA feature card.                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | OPMA feature card—This is a feature board that contains the majority of the management subsystem hardware. The term "mCard" (management card) is often used for this in the interest of brevity.                                                                                                                                                                                                                                                                                                                        |

|         | OPMA connector—This is the connector into which an OPMA feature card (mCard) is plugged to provide a given system hardware management feature set.                                                                                                                                                                                                                                                                                                                                                                      |

|         | OPMA interface—This refers collectively to all OPMA signals that are routed to and from the OPMA connector. The term "interface" as used in this document refers to an electrical interface as opposed to software or command interfaces.                                                                                                                                                                                                                                                                               |

| OSPM    | Operating System directed Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PLD     | Programmable Logic Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| POST    | Power On Self Test. In this specification, POST refers to code run at boot time by the BIOS on a server.                                                                                                                                                                                                                                                                                                                                                                                                                |

| PWM     | Pulse Width Modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RxD     | Receive Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SCI     | System Control Interrupt. This is a way to notify the ACPI subsystem that a device is requesting service.                                                                                                                                                                                                                                                                                                                                                                                                               |

| SDR     | Sensor Data Record. See the IPMI specification for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SDRR    | Sensor Data Record Repository                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SEEPROM | Serial Electrically Erasable Programmable Read-Only Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SEL     | System Error Log. See the IPMI specification for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SERIRQ  | Serialize Interrupt Request. See the LPC specification for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SMBus   | An I <sup>2</sup> C bus derivative.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SMI     | System Management Interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SMIC    | IPMI's Server Management Interface Chip command interface                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SoL     | Serial over LAN. The redirecting of text data to a remote text console using Ethernet as a transport. Redirected text is typically the BMC's CLI or system-generated text such as BIOS boot and setup screens.                                                                                                                                                                                                                                                                                                          |

| SPD     | Serial Presence Detect (used for DRAM auto sizing)                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

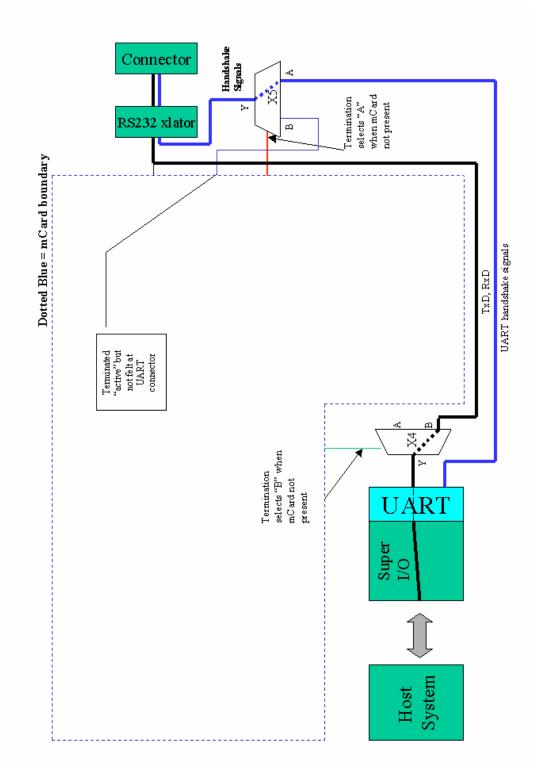

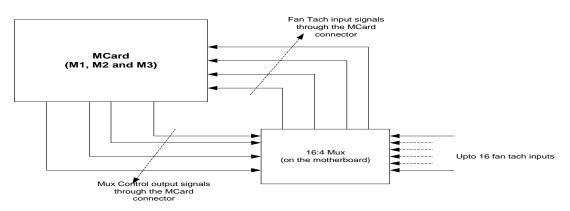

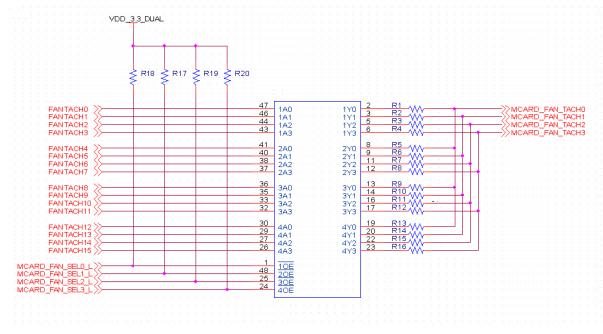

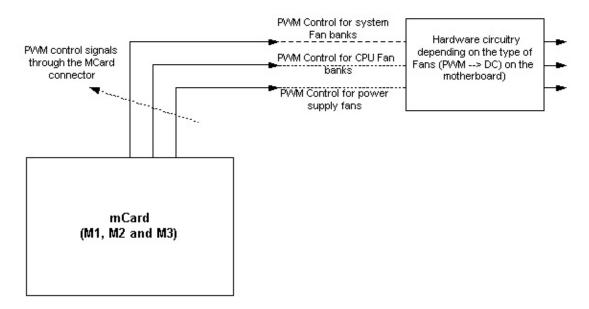

| SSIF    | IPMI's SMBus System InterFace command interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |